- #8088 5MHZ MEMORY SPEED NS HOW TO#

- #8088 5MHZ MEMORY SPEED NS CODE#

- #8088 5MHZ MEMORY SPEED NS FREE#

Some of the instructions for protected mode can (or must) be used in real mode to set up and switch to protected mode, and a few (such as SMSW and LMSW) are useful for real mode itself. The 80286 also added new instructions for protected mode: ARPL, CLTS, LAR, LGDT, LIDT, LLDT, LMSW, LSL, LTR, SGDT, SIDT, SLDT, SMSW, STR, VERR, and VERW. The 80286 included, in addition to all of the 8086 instructions, all of the new instructions of the 80186: ENTER, LEAVE, BOUND, INS, OUTS, PUSHA, POPA, PUSH immediate, IMUL immediate, and immediate shifts and rotates. Also, the 80286 was more efficient in the prefetch of instructions, buffering, execution of jumps, and in complex microcoded numerical operations such as MUL/ DIV than its predecessor. They were performed by a dedicated unit in the 80286, while the older 8086 had to do effective address computation using its general ALU, consuming several extra clock cycles in many cases. This was partly due to the non-multiplexed address and data buses, but mainly to the fact that address calculations (such as base+index) were less expensive. This was a large increase, fully comparable to the speed improvements seven years later when the i486 (1989) or the original Pentium (1993) were introduced. The performance increase of the 80286 over the 8086 (or 8088) could be more than 100% per clock cycle in many programs (i.e., a doubled performance at the same clock speed). It was produced in a 68-pin package, including PLCC ( plastic leaded chip carrier), LCC ( leadless chip carrier) and PGA ( pin grid array) packages. It had 134,000 transistors and consisted of four independent units: the address unit, bus unit, instruction unit, and execution unit, organized into a loosely coupled (buffered) pipeline, just as in the 8086. The CPU was designed for multi-user systems with multitasking applications, including communications (such as automated PBXs) and real-time process control. Intel did not expect personal computers to use the 286. Intel second sourced this microprocessor to Fujitsu Limited around 1985. This E-2 stepping part may have been available in later 1986.

#8088 5MHZ MEMORY SPEED NS FREE#

The later E- stepping level of the 80286 was free of the several significant errata that caused problems for programmers and operating-system writers in the earlier B-step and C-step CPUs (common in the AT and AT clones).

The 6 MHz, 10 MHz, and 12 MHz models were reportedly measured to operate at 0.9 MIPS, 1.5 MIPS, and 2.66 MIPS respectively.

#8088 5MHZ MEMORY SPEED NS CODE#

On average, the 80286 was reportedly measured to have a speed of about 0.21 instructions per clock on "typical" programs, although it could be significantly faster on optimized code and in tight loops, as many instructions could execute in 2 clock cycles each. Intersil and Fujitsu also designed fully static CMOS versions of Intel's original depletion-load nMOS implementation, largely aimed at battery-powered devices. AMD and Harris later produced 16 MHz, 20 MHz and 25 MHz parts, respectively. "Since AO is used to select the low bank of memory, we are only left with 19 bits of address and therefore we can only map 512KB of memory", do you agree with that statement and why? (10 point) 8.Intel's first 80286 chips were specified for a maximum clockrate of 5, 6 or 8 MHz and later releases for 12.5 MHz. Looking at the diagram below, why is it important to add the latch to 10/M, RD', and WR when it doesn't do any demultiplexing? (10 point). Explain in your own words and using diagrams: how does address row/column multiplexing in DRAM (10 point) 6. In your own words, explain why different data banks of ROM sections do not require bank selection using AO, BHE or other signals (10 point) 5.

#8088 5MHZ MEMORY SPEED NS HOW TO#

Using Separate Bank Write Strobe methodology, draw a diagram to show how to connect an 8086 microprocessor to 128KB of RAM starting at address E0000H and using 64K x 4 SRAM chips. Using Separate Decoders methodology, show how to connect an 8086 microprocessor to 128KB of RAM using as many 64K x 8 SRAM chips as needed.

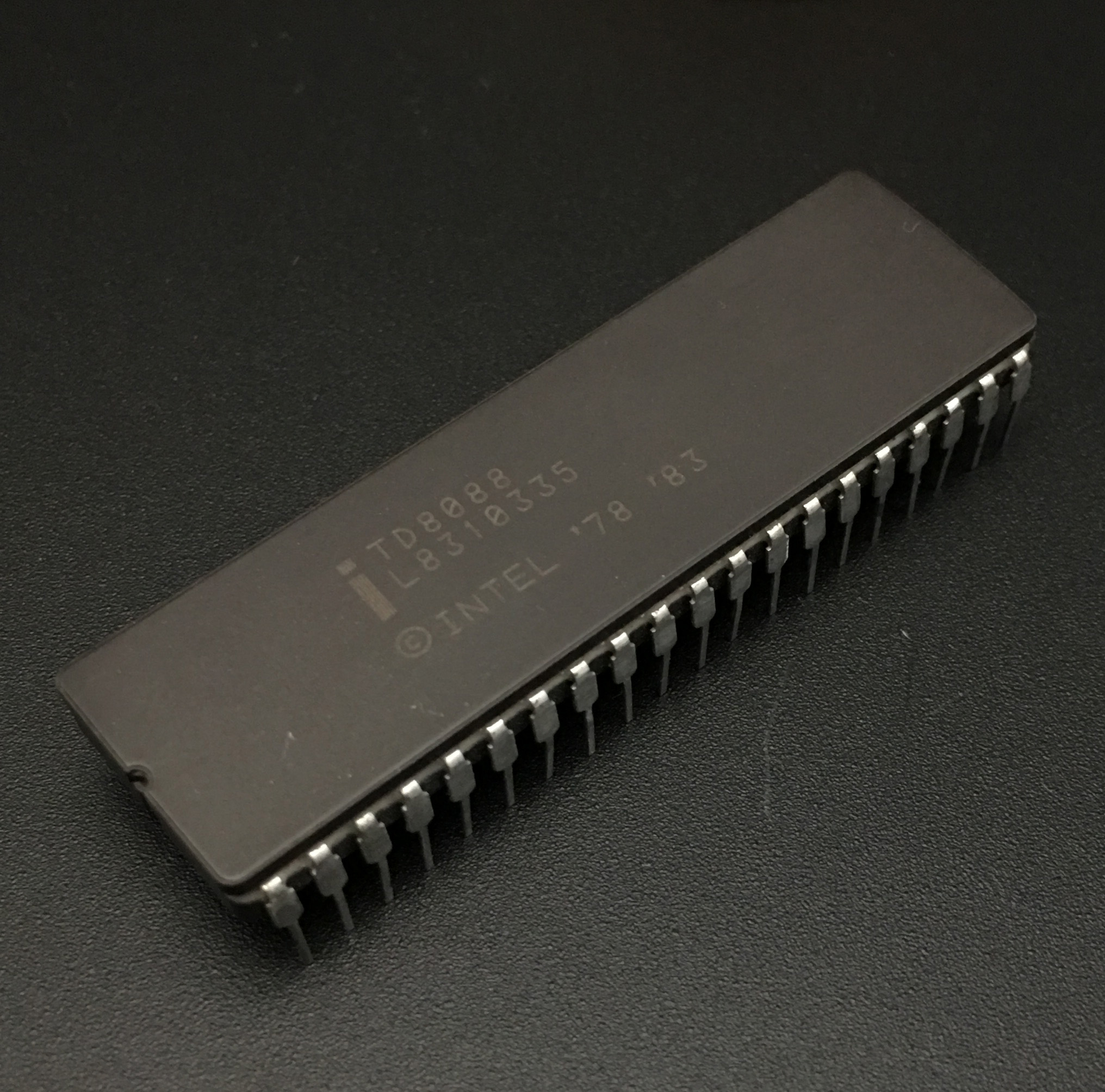

The chips are to be placed at address 00000H and PLD is the only available option for decoding. Using a diagram, illustrate how to properly organize 256KB of ROM made of 64K x 8 chips connected to 8088 microprocessor, knowing that the chips have access time of 600 ns and the processor operates at 5MHz clock rate.

0 kommentar(er)

0 kommentar(er)